Introduction

The development of complex hardware/software systems is a time-consuming and resource-intensive process that requires extensive testing and verification. The growing complexity of the systems has made simulation for verification increasingly difficult and slow.

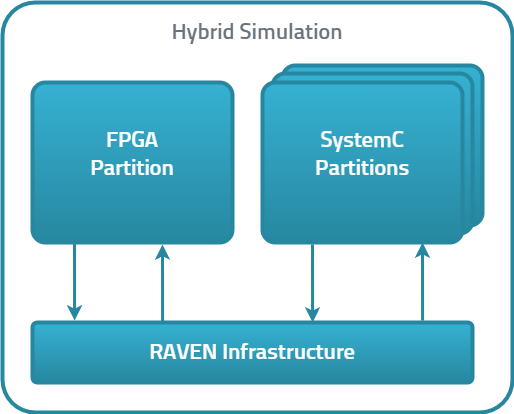

RAVEN allows to speed up SystemC simulations through coarse-grained parallelization. Even more important RAVEN infrastructure enables the co-simulation of SystemC and RTL mapped onto FPGA. The development of an embedded hardware project rarely starts from scratch. Typically, there are previous projects with reusable hardware components that should be integrated into the verification of new elements as soon as possible. Addressing this need, RAVEN aims to accelerate project development by enabling hybrid simulation. Hybrid simulation is a parallel simulation of a hardware design partly on FPGA and partly in SystemC. RAVEN enables the integration of existing RTL components using an FPGA, while simultaneously running new system components as a Virtual Prototype on the host.

RAVEN

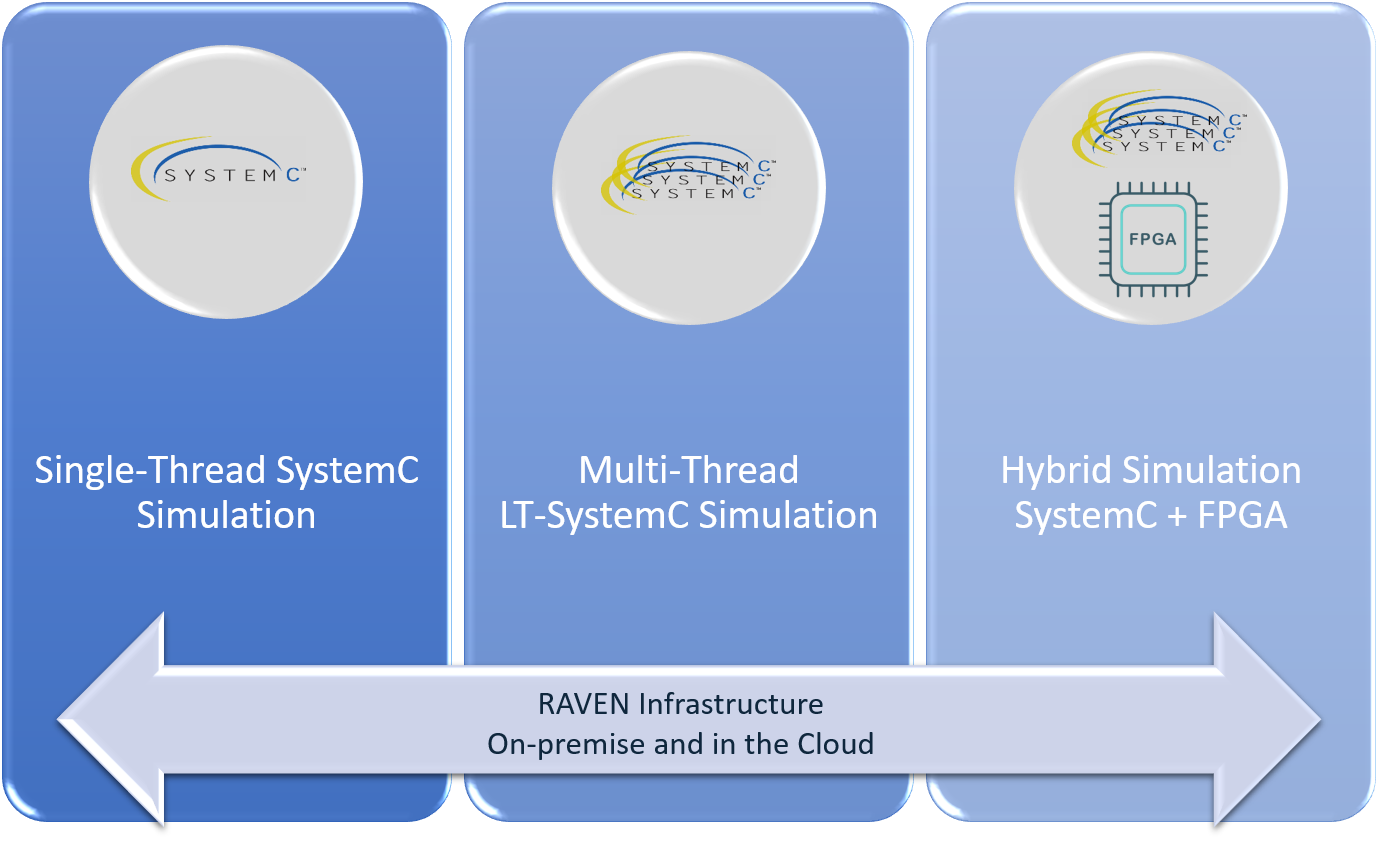

RAVEN supports different simulation options to enable more efficient and accurate hardware/software development.

- Single-threaded SystemC simulation The adjustments made to the SystemC kernel for parallel SystemC and Hybrid Simulation were carefully designed to ensure backward compatibility, allowing conventional single-threaded SystemC simulations to remain fully supported.

- Multi-threaded parallel simulation RAVEN provides an infrastructure that enables multi-threaded parallel SystemC simulation for loosely timed partitions.

- Hybrid simulation of SystemC and FPGA The highlight of RAVEN is its hybrid simulation capability, which combines the advantages of both SystemC simulation and FPGA prototyping. This approach achieves the best acceleration and significantly reduces simulation time, but provides only limited debugging options. To circumvent this, RAVEN offers the possibility to generate and simulate the FPGA RTL in a hybrid manner with Verilator instead of the FPGA.

RAVEN offers the flexibility to run parallel and hybrid simulations either locally on-premise or in the cloud. Cloud simulation provides scalable and cost-efficient access to a wide range of computing resources and alleviates the need for upfront hardware investments and maintenance. A graphical user interface assists the user with the setup, configuration and execution of the simulation in the Cloud.

Hybrid Simulation

- Challenge

The development of an embedded hardware project rarely starts from scratch. Typically, there are previous projects with reusable hardware components that should be integrated into the verification of new elements as soon as possible. The problem is that there is no easy way to simulate RTL design together with a Virtual Prototype. - Problem with Traditional Methods

SystemC can only be executed in a single process and does not benefit from modern multi-core processors. Moreover, OSCI SystemC does not provide the possibility to synchronize with FPGA simulation. It makes the SystemC simulator a performance bottle-neck for complex VP projects. - Solution:

Hybrid simulation is interesting for customers who already have RTL and want to extend or replace part of the design (for example by introducing a RISC-V TGC core). Our solution enables the integration of existing RTL components using an FPGA, while simultaneously running new system components as a Virtual Prototype on the host. This allows our customers to easily simulate existing hardware in parallel with a virtual prototype.

Hybrid Simulation is completely integrated and fully combinable with other MINRES products and services like the open source SystemC Components (SCC) productivity library. Last but not least, our hybrid simulation solution allows cost savings combined with high reliability and scalability by enabling hybrid simulation in the AWS Cloud.