Virtual Prototyping and Platform Modeling

MINRES provides VP modelling services for early SW development and architectural exploration. These sevices are backed by our own environment and open-source libraries. We have a successful track-record by leading semiconductor companies.

Virtual hardware models enable Shift Left in the project development cycle. By using virtual prototypes, the firmware is ready much earlier and fits perfectly with the hardware even before the silicon is available, which also greatly simplifies and accelerates the hardware build. With the help of Virtual Platforms, the firmware can be developed in parallel with the hardware. This enables continuous engineering, i.e. improvements identified during firmware development and verification can be applied to hardware immediately, even before the first silicon is available. As a result, HW and FW are better aligned and the number of tapeouts is reduced, resulting in significant cost savings.

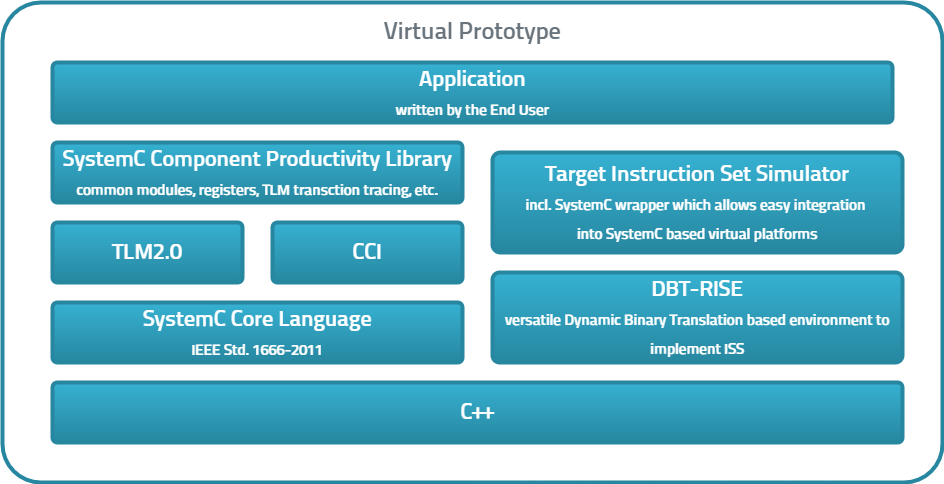

We have extensive expertise in the development of SystemC based Virtual Prototypes. We have years of experience in building Eclipse-based VP development environments and our SystemC Components productivity library is used by several renowned SoC vendors.

DBT-RISE (Dynamic Binary Translation) is the basis for our Virtual Platforms and allows to quickly setup RISC-V or other architecture Instruction Set Simulators. DBT-RISE uses a generative approach, which allows the generation of any required combinations or user-defined extensions for an ISS.

Some of our OpenSource projects are explicitly listed on systemc.org