Accelerate SoC Development with MINRES Flexible, Scalable IP

Why Development Teams Choose MINRES hardware IP

- MINRES software-driven approach boosts productivity and speed

- Accelerated time-to-market through reusable IP and tooling

- Open standard RISC-V ISA cores for long-term independence and ecosystem support

- EDA-vendor agnostic implementation

- Backed by modern verification methods and concise documentation

The Good Folk Series

The Good Folk Series (TGFS) is a growing family of trustworthy, generator-based and flexible hardware IP, created to offer reliable IP solutions tailored to exactly meet the system requirements. Each IP block is designed to integrate seamlessly into your project, reducing development effort and ensuring performance exactly where it matters most.

The innovative software-driven hardware IP is developed with state-of-the-art processes and tools and a strong focus on methodological competence and quality that are key elements of our company culture. Safety and security awareness at each step ensure operational integrity, full transparency and traceability throughout the IP life-cycle. High quality deliverables and concise documentation facilitate the IP integration into the target system.

The Good Folk Series Consists of 3 Building Blocks:

- The Good Cores (TGC): A family of flexible RISC-V processor cores

- Moonlight: A configurable and extendable subsystem, which complements TGC with memories, an interconnect infrastructure as well as various peripherals and controllers

- The Good Accelerator (TGA): A generator-based machine learning accelerator

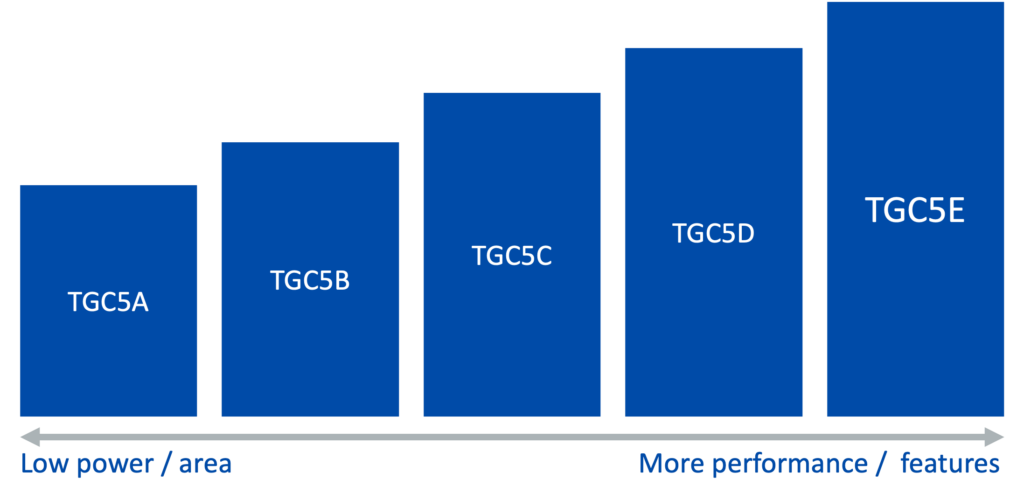

The Good Cores (TGC)

At the heart of The Good Folk Series (TGFS) are The Good Cores (TGC), a highly flexible, scalable and extendable RISC-V core family from MINRES. TGC enable you to build exactly the SoC you need – no more, no less – resulting in better performance per watt and optimal silicon area usage. The open standard RISC-V ISA and the growing ecosystem around it guarantee the continuity and sustainability of the TGC IPs. It is best suited for low-power applications in IoT and edge applications.

TGC processors are available in five standard configurations, each available in 32-bit or 64-bit. They all are Harvard, single issue in-order pipelines, with either 3, 4 or 5 stages.

TGC*A

The smallest core of the TGC family targets state machine controllers. It is best suited for embedded systems with low power and low area requirements.

Details

- RV32E or RV64E Zicsr Zifencei (16 GPR)

- 3 stage, single issue in-order pipeline

- No caching or branch prediction

- Machine mode only

- CLINT and wait for interrupt (WFI) support

- Memory bus interface: AHB3 Lite, AXI4, AXI4Lite, OCP, and OBI 1.0

TGC*B

This 3-stage pipeline RV32I or RV64I core is best suited for embedded systems as it supports RTOS, still having reduced area and power consumption.

Details

- RV32I or RV64I Zicsr Zifencei

- 3 stage, single issue in-order pipeline

- Machine mode only

- CLINT & wait for interrupt (WFI) support

- Memory bus interface: AHB3 Lite, AXI4, AXI4Lite, OCP, and OBI 1.0

TGC*C

For Edge and IoT applications, this 4-stage RV32IMC or RV64IMC core offers the basic capabilities.

Details

- RV32IMC or RV64IMC Zicsr Zifencei

- Machine mode only

- 4 stage, single issue in-order pipeline

- CLINT & wait for interrupt (WFI) support

- Memory bus interface: AHB3 Lite, AXI4, AXI4Lite, OCP, and OBI 1.0

TGC*D

When dense hardware-software coupling is required for Edge and IoT applications, this 4-stage RV32IMC or RV64IMC core integrates configurable and extendable CLIC and PMP capabilities.

Details

- RV32IMC or RV64IMC Zicsr Zifencei

- Machine & User mode

- 4 stage, single issue in-order pipeline

- CLIC + wait for interrupt (WFI) support

- Memory bus interface: AHB3 Lite, AXI4, AXI4Lite, OCP, and OBI 1.0

- Physical memory protection (PMP)

TGC*E

The largest of the standard configurations is the choice for IoT or Edge applications with high frequency requirements. It has the capabilities of TGC*D in a 5-stage pipeline.

Details

- RV32IMC or or RV64IMC Zicsr Zifencei

- Machine & User mode

- 5 stage, single issue in-order pipeline

- No caching or branch prediction

- CLIC + wait for interrupt (WFI) support

- Memory bus interface: AHB3 Lite, AXI4, AXI4Lite, OCP, and OBI 1.0

- Physical memory protection (PMP)

Optional features:

Many other helpful features can be integrated if required:

Details

- LR/SC support (part of A extension)

- Custom instructions

- Non-maskable interrupts (NMI)

- Safety features: ECC, parity and lockstep

- Cache support

- Branch prediction

- Trace and debug capabilities

- Hart to encoder trace interface

- User mode (U extension)

- User level interrupts (tentatively reserved N extension)

What’s Next in The Good Folk Series?

Moonlight

For applications and projects that require complete subsystems, MINRES is expanding its portfolio with Moonlight – a configurable and extendable subsystem built around a TGC. Moonlight lets you jumpstart development with a pre-integrated, pre-verified foundation, reducing setup times and simplifying project scoping. At its heart, a freely customizable TGC variant offers the processing capabilities, which is complemented by memories, an interconnect infrastructure as well as various peripherals and controllers.

For connecting TGC with the memory system, we have used an AMBA-compatible high-speed bus supporting AXI4, AXI4Lite, AHB3. It furthermore connects the peripheral bus via a bus bridge, where the type and number of peripherals can be configured (e.g., GPIO, UART, Timer, SPI, I2S). Moonlight also enables the integration of additional components like DMA or interrupt controllers.

This configurability and flexibility of Moonlight is enabled by a generator-based approach, which allows for a fast composition of the target system by selecting the required components as well as quickly integrating project-specific IPs, e.g., targeting machine learning applications like The Good Accelerator (TGA).

Available soon, but please contact us now to discuss your requirements.

The Good Accelerator for Edge AI/ML Applications

The Good Accelerator (TGA) is a flexible hardware IP block that offloads demanding deep neural network functions from the CPU, lowering power usage and freeing up processing capacity, ideal for Edge AI / Machine Learning applications. It is loosely coupled, so it can be combined with any processor. It supports both standalone and joint use with other components of The Good Folk Series. Using a generator-based approach, TGA creates customized hardware models that match specific applications, making it easier to optimize both the ML model and the hardware together. This allows you to build AI-enabled SoCs that deliver high performance without draining your power budget.

Coming soon, please register your interest.

Build Smarter

With The Good Folk Series and the MINRES methodology, your team stays in control, while gaining speed, safety, and structure. Whether you need a fast proof of concept or a robust product-grade SoC, our approach helps you deliver on time and at scale.

Get in touch to explore how we can support your next SoC project.