Unlocking the Power of Virtual Platforms in SoC Development: From Pre- to Post-Silicon

As System-on-Chip (SoC) designs become increasingly complex, development teams are under growing pressure to deliver high-performance, software-rich silicon solutions with faster time-to-market and fewer costly mistakes. To stay competitive, the industry has embraced methodologies that allow teams to “shift left” in the development cycle. One of the most powerful enablers of this shift is the virtual platform (VP).

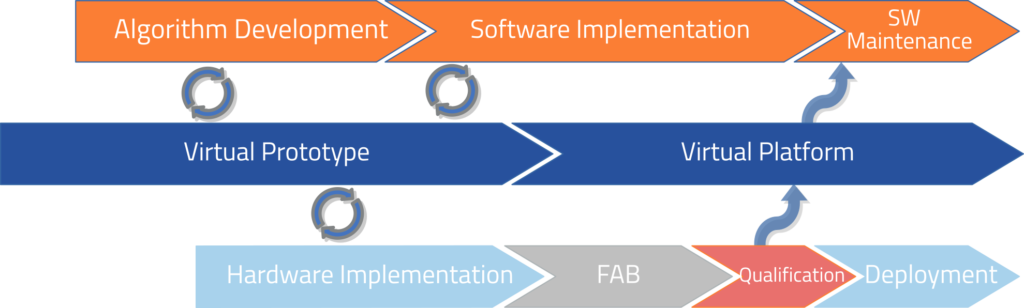

A virtual prototype or virtual platform, commonly referred to as a VP, is a high-level software model of a hardware system that is usually created using abstraction layers such as SystemC and TLM-2.0. It captures the functional behavior of processors, memories, peripherals, and interconnects, enabling complete software stacks to run in a simulated environment. The utility of virtual platforms spans both the pre-silicon and post-silicon phases of SoC development, making them indispensable tools for engineering teams striving for first-time-right silicon and accelerated product readiness.

In the pre-silicon phase, virtual prototypes allow software teams to begin development months before physical hardware becomes available. This means engineers can write and test bootloaders, operating systems, and application code without waiting for RTL to be finalized or silicon to return from the fab. Not only does this accelerate software maturity, but it also de-risks the project by uncovering bugs that might otherwise go undetected until integration. Hardware-software co-design becomes far more feasible, as VPs allow both domains to iterate in parallel. Issues like interrupt handling, memory map alignment, or register interface mismatches can be discovered early, giving architects valuable time to adapt.

Moreover, virtual prototypes serve as an ideal vehicle for architectural exploration. Design teams can experiment with different core configurations, memory hierarchies, and bus architectures to evaluate the trade-offs between performance, power, and area. These insights help shape the final RTL and improve design efficiency without the overhead of gate-level simulations.

Even after the arrival of silicon, when virtual prototypes become virtual platforms due to their now solid nature, they continue to offer tangible value. VPs provide a reliable reference environment for bring-up and hardware validation, where teams can compare silicon behavior against the modeled expectations. This is especially helpful for isolating subtle hardware bugs or inconsistencies during initial lab testing. Software regression and integration testing can also continue in parallel, without monopolizing valuable hardware resources. For teams managing geographically distributed software groups, the ability to run simulations in the cloud ensures uniform test coverage and scalability.

Another compelling use case for VPs in the post-silicon phase is their ability to simulate scenarios that are impractical or unsafe to recreate on real hardware. Fault injection, power failures, or misbehaving peripherals can be explored in a controlled virtual environment. This is particularly relevant for domains like automotive and aerospace, where safety compliance depends on rigorous validation of rare or catastrophic events. Virtual platforms also simplify training and customer enablement by allowing partners or clients to experiment with a system model without needing physical access to boards or lab environments.

Across the industry—and within MINRES Technologies—virtual prototypes and virtual platforms have proven their worth in enabling earlier software delivery, reducing risk, and maintaining velocity beyond tape-out. By acting as a persistent companion throughout the SoC development journey, they unify the traditionally siloed efforts of hardware and software teams, creating a more cohesive and agile design process.

Ultimately, the value of a virtual prototype or virtual platform lies in its longevity and adaptability. From the earliest specification sketches to full system integration and deployment, it continues to serve as a critical touchpoint. In an era of increasing system complexity and ever-tightening timelines, VPs are no longer a luxury—they are a necessity for engineering success.

If you’re looking to boost development speed, reduce cost, and deliver reliable products faster, then virtual prototypes and virtual platforms are a proven solution—and we’re here to help you make the most of them.

Ready to virtualize your SoC development? Contact us to learn more about our platform modeling services and simulation solutions.