In modern hardware design, systems evolve through multiple levels of abstraction before reaching silicon. Each stage adds more detail, constraints, and implementation accuracy.

In the early stages, engineers focus on functionality and architecture exploration and SystemC TLM (Transaction-Level Modeling) plays an important role. Fast simulation speeds allow designers to evaluate architectural decisions and communication schemes without being constrained by low-level details.

As the design matures, the focus shifts to implementation accuracy. This is where RTL (Register Transfer Level) becomes essential. RTL describes the hardware at a cycle-accurate level – it’s the foundation for FPGA prototyping and ASIC synthesis.

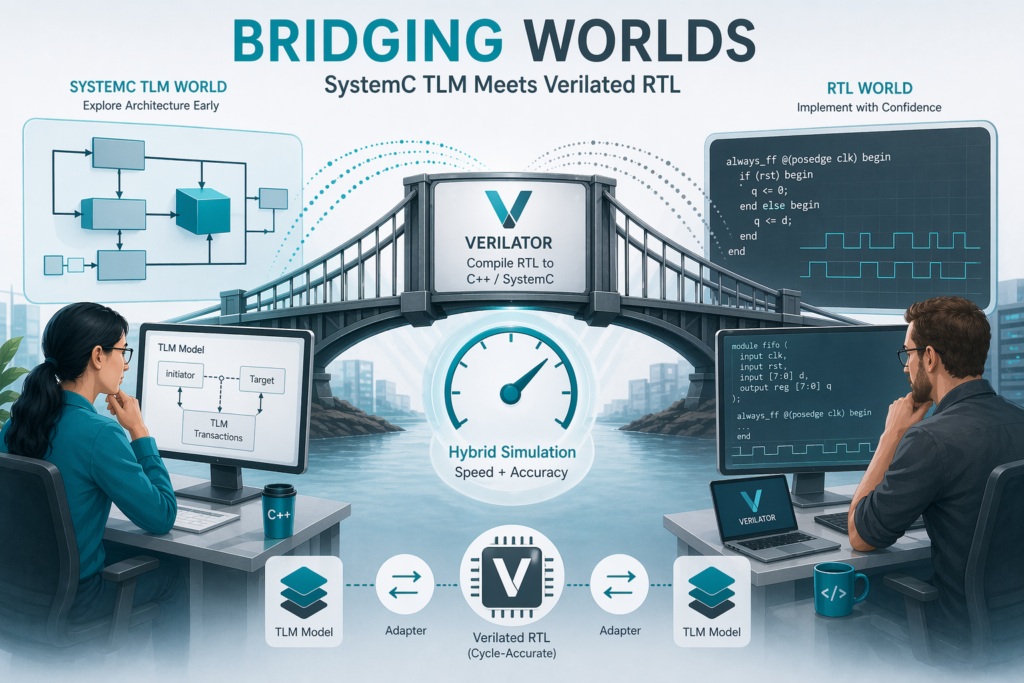

SystemC TLM and RTL development can appear to be two parallel but independent tracks: SystemC for high-level modeling; RTL for hardware implementation. In fact, they are complementary. Bridging these two worlds enables engineers to combine speed and accuracy which is critical for modern SoC development.

So where does Verilator help?

Most RTL designs are written in Verilog, SystemVerilog, or VHDL. Traditionally, simulating RTL requires HDL simulators, such as VCS, ModelSim or Questa. These tools are powerful, but have their limitations such as performance bottlenecks, limited software integration or scalability issues.

This is where Verilator can be particularly powerful.

Verilator is not a traditional simulator, but a compiler which translates synthesizable Verilog or SystemVerilog into optimized C++ or SystemC models. By converting RTL design into C++, Verilator opens the door to hybrid simulation platforms, which consist of SystemC TLM models and models with cycle-accurate behavior.

HYPRSENSE: A Broader Perspective

Today, Verilator supports Verilog and SystemVerilog. The HYPRSENSE project is extending Verilator with VHDL support contributed by MINRES, which will further broaden its applicability and make it even more attractive.

Depending on the complexity of design, different strategies such as flat model or hierarchical model of design are exploited to improve the verilation process. In addition, the team is examining multithreading to accelerate the simulation of the verilated model.

How Verilated RTL Fits into a SystemC TLM Platform

One of the main challenges in building a hybrid simulation platform is integration. The SystemC model generated from an RTL design is typically expressed at the sc_signal level, while the rest of the virtual platform often operates at the TLM level. This mismatch requires adapters at the boundary to convert higher-level transactions into signal activity across one or more cycles and the inverse.

This is where the MINRES SystemC Components Library (SCC) becomes invaluable. The SCC offers pin-level adapters and infrastructure to help bridge this gap. With the SCC, the verilated block can be integrated into a broader SystemC platform in a clean and reusable manner.

The Value of Combining SystemC TLM and Verilated RTL

The combination of SystemC TLM and verilated RTL creates a practical methodology for both design and verification.

At MINRES, this methodology has already been applied successfully in several areas. One case is the verification of modeled IP, where the verilated RTL models serve as a gold reference standard for verifying higher-level SystemC model. In the subsequent projects, the verified test bench can uncover the hidden bugs of the verilated RTL model from the new design.

Another application is the MINRES cross-level functional TGC verification, where the UVM testbench integrate the ISS as a reference for the verification of functional correctness in our RISC-V cores. This approach enables robust functional verification of TGC across different levels of abstraction. My colleague Stansilaw Kaushanski presented on the topic of the ‘Automated Cross-level Verification Flow of a Highly Configurable RISC-V core at the RISC-V Summit Europe 2023 – you can view the presentation online. If you are interested in this approach, please contact us.

In both cases, automating the simulation and verification flow has proven extremely valuable. Once established, the flow can be rapidly adapted and repurposed for new projects, significantly reducing setup time and improving productivity.