At MINRES, we are always trying to find ways to improve hardware design productivity, verification workflows, and system-level integration – and in doing so end up evaluating a lot of emerging technologies. We have recently been working on one that we would like to share: we translated an existing VHDL implementation of a pipelined RISC-V processor into RHDL, synthesized it and ran it on an FPGA.

RHDL is a hardware description language based on Rust. It follows earlier work on RustHDL, which allowed FPGA firmware to be described in Rust and compiled to Verilog for standard synthesis tools. RHDL was really a substantial redesign of that approach, rewritten from the ground up to enable higher-performance simulation, more natural Rust syntax, easier reuse, and improved support for Rust language features such as enums with payloads.

These new features made RHDL an interesting candidate for evaluating whether Rust-based hardware descriptions can be used for real-world RTL development. The project is still evolving, but there are some really positive steps forward and it’s already providing a useful basis for practical experimentation with synthesizable hardware designs.

The design used in this evaluation is based on the pipelined RISC-V architecture presented in Harris & Harris: Digital Design and Computer Architecture. It implements the classical five pipeline stages:

Instruction fetch

Decode

Execute

Memory, and

Write-back

It also includes a hazard unit for forwarding, stalls, and pipeline flushes.

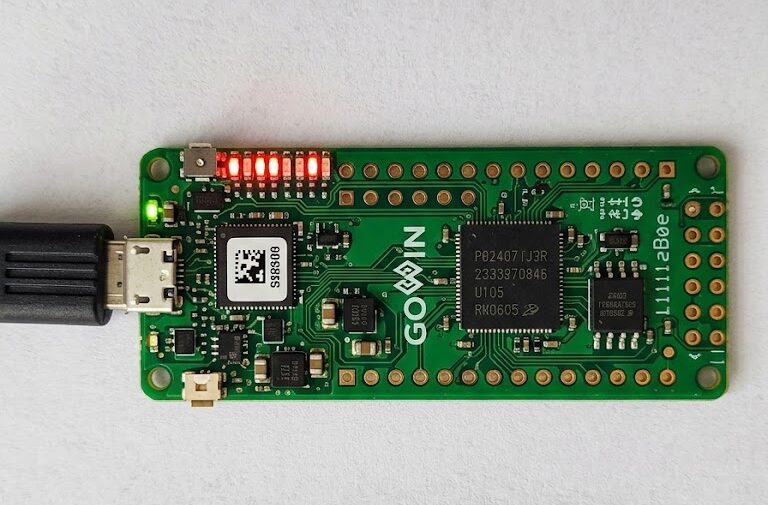

To support a tangible FPGA demonstration, the design was extended with a memory router and a small memory-mapped GPIO device. This allowed a RISC-V binary counter program to drive the eight LEDs on the board. The objective was to evaluate RHDL on a realistic RTL design rather than on a simple xor gate or half adder. A pipelined processor brings together hardware design patterns such as pipeline registers, datapath components, control logic, memory interfaces, inter-stage signal propagation, and peripheral access.

We kept the RHDL structure close to the original VHDL implementation. VHDL entities and architectures were mapped to RHDL modules, pipeline registers were represented explicitly, and sequential logic was translated with attention to clocking, reset, and enable behavior.

After translation, the generated design was synthesized for FPGA, specifically the Trenz TEC0117 board. This confirmed that the evaluation was not limited to syntax or simulation, but could be taken through a conventional FPGA synthesis flow and integrated with board-specific constraints, clocking, reset handling, memory mapping, and GPIO output.

For this experiment, the complete board toolchain was not implemented directly inside the RHDL crate. Instead, we passed the generated Verilog through a Yosys-based synthesis flow. This kept the downstream integration flexible: board-specific support could be added externally without depending on immediate integration into the RHDL project itself.

Using the existing VHDL implementation as a reference made the translation process more controlled. It provided a known architecture, clear module boundaries, and a baseline to simplify reviewing the structure which was generated.

The translation revealed some challenges. RHDL documentation is still at an early stage and still evolving, so some aspects required a bit of experimentation. In addition, some subcircuits we had initially implemented (purely as combinational blocks) had to be restructured because we couldn’t find a good way to connect them directly into the surrounding sequential circuit as we had hoped.

Another challenge was clocking behavior. The original VHDL design used the negative clock edge for register-file write-back. We could not find a suitable way to model this negative-edge behavior directly in RHDL, so we modified the design slightly to avoid relying on the negative edge. In other words, translating between hardware description languages is not only a syntactic exercise: Synthesis intent, clocking model, and circuit structure must also be explicitly handled.

This RHDL evaluation is the first step in our broader plan to compare modern hardware description approaches to find out which HDL is best suited to which design cases. We are already planning to look more into other languages and frameworks, such as Spade and other emerging RTL design tools, and see how they stack up against comparable designs.

For MINRES, these evaluation projects help us to keep on top of understanding the design choices our clients face with modern hardware design methodologies – ultimately, we like to be sure we have explored all options (including emerging languages and methodologies) to help our customers and partners to achieve efficient, maintainable, and verifiable digital design workflows.